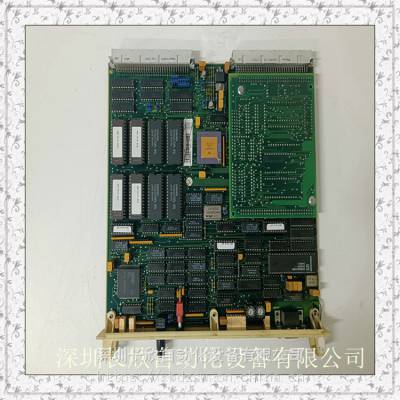

PFSK130 3BSE002616R1工控DCS系统备件PFSK系列信号处理器即使在传统DSP之间比较MIPS大小也具有一定的片面性。例如,某些处理器允许在单个指令中同时对几位一起进行移位,而有些DSP的一个指令只能对单个数据位移位;有些DSP可以进行与正在执行的ALU指令无关的数据的并行处理(在执行指令的同时加载操作数),而另外有些DSP只能支持与正在执行的ALU指令有关的数据并行处理;有些新的DSP允许在单个指令内定义两个MAC。因此仅仅进行MIPS比较并不能准确得出处理器的性能。解决上述问题的方法之一是采用一个基本的操作作为标准来比较处理器的性能。常用到的是MAC操作,但是MAC操作时间不能提供比较DSP性能差异的足够信息,在绝大多数DSP中,MAC操作仅在单个指令周期内实现,其MAC时间等于指令周期时间,某些DSP在单个MAC周期内处理的任务比其它DSP多。MAC时间并不能反映诸如循环操作等的性能,而这种操作在所有的应用中都会用到。通用的办法是定义一套标准例程,PFSK130 3BSE002616R1工控DCS系统备件PFSK系列信号处理器比较在不同DSP上的执行速度。这种例程可能是一个算法的“核心”功能,如FIR或IIR滤波器等,也可以是整个或部分应用程序,如语音编码器等。在比较DSP处理器的速度时要注意其所标榜的MOPS(百万次操作每秒)和MFLOPS(百万次浮点操作每秒)参数,因为不同的厂商对“操作”的理解不一样,指标的意义也不一样。例如,某些处理器能同时进行浮点乘法操作和浮点加法操作,因而标榜其产品的MFLOPS为MIPS的两倍。其次,在比较处理器时钟速率时,DSP的输入时钟可能与其指令速率一样,PFSK130 3BSE002616R1工控DCS系统备件PFSK系列信号处理器也可能是指令速率的两倍到四倍,不同的处理器可能不一样。另外,许多DSP具有时钟倍频器或锁相环,可以使用外部低频时钟产生片上所需的高频时钟信号。

PFSK130 3BSE002616R1 The word width of all floating point DSP is 32 bits, while that of fixed point DSP is generally 16 bits. There are also 24 bit and 20 bit DSP, such as Motorola's DSP563XX series and Zoran's ZR3800X series. Since the word width has a great relationship with the external size of DSP, the number of pins and the size of memory required, the word width directly affects the cost of devices. The wider the word width is, the larger the size is. The more pins are, PFSK130 3BSE002616R1the larger the memory requirements are, and the cost increases accordingly. Under the condition of meeting the design requirements, DSP with small word width should be selected as far as possible to reduce the cost.PFSK130 3BSE002616R1When selecting fixed point and floating point, you can balance the relationship between word width and development complexity. For example, PFSK130 3BSE002616R1 a 16 bit word width DSP device can also implement a 32-bit word width double precision algorithm by combining instructions. This method is also feasible if single precision can meet most computing requirements, while only a few codes require double precision. However, if most computing requirements require high precision, processors with large word width should be selected.Please note that the width of the instruction word and data word of most DSP devices is the same, but there are also some differences. For example, PFSK130 3BSE002616R1the data word of ADSP-21XX series of ADI is 16 bits and the instruction word is 24 bits.Whether the processor meets the design requirements depends on whether it meets the speed requirements. There are many ways to test the speed of the processor, the most basic is to measure the instruction cycle of the processor.However, the instruction execution time does not indicate the real performance of the processor. Different processors can complete different tasks in a single instruction. Simply comparing the instruction execution time cannot just distinguish the difference in performance. Some new DSPs use a very long instruction word (VLIW) architecture. In this architecture, PFSK130 3BSE002616R1multiple instructions can be implemented in a single cycle time, and each instruction performs fewer tasks than traditional DSPs. Therefore, PFSK130 3BSE002616R1compared with VLIW and general DSP devices, comparing the size of MIPS can be misleading.

模块库存1766-L32BWAA欢迎采购

¥1987.00

模块库存1766-L32BWAA欢迎采购

¥1987.00

模块库存2711P-RN6欢迎采购

¥1987.00

模块库存2711P-RN6欢迎采购

¥1987.00

模块库存1756-PB72欢迎采购

¥1987.00

模块库存1756-PB72欢迎采购

¥1987.00

模块库存1756-CN2R欢迎采购

¥1987.00

模块库存1756-CN2R欢迎采购

¥1987.00

模块库存1756-PA72欢迎采购

¥1987.00

模块库存1756-PA72欢迎采购

¥1987.00